고효율 태양광 인버터 실현할 전력 변환 회로

이 프로젝트의 개발 목표는 스크루 타입의 모듈로 된 100kW 이상의 전력 애플리케이션에서의 스위칭 손실의 감소다. 이러한 애플리케이션의 한계는 주로 스트레이 인덕턴스와 다이오드의 역회복 동작에 의한 기생 효과에 있다. 기생 인덕턴스에 의한 과전압 스파이크는 턴오프 스위칭 속도를 제한한다. 프리휠링 다이오드의 역회복 동작으로 인한 손실 및 증가된 전자파(EMI)는 턴온 스위칭 속도의 증가에 있어 걸림돌이 된다.

스위칭 손실 감소를 위해서는 턴오프시 인덕턴스의 최소화와 턴온 손실의 감소가 무엇보다 중요하다. 이러한 과정은 턴오프 동작에는 낮은 인덕턴스를 유지할 수 있게 하며, 기생 인덕턴스를 활용함으로써 턴온 손실의 감소를 실현시킨다. 이어서 스위칭 손실 감소를 위한 세 번째 행동은 중성점 클램핑(NPC) 인버터 토폴로지, 그리고 마지막으로 IGBT와 MOSFET의 병렬연결 토폴로지는 이 아이디어에 대한 발전된 전망을 보여준다.

스위칭 손실 이론

전력·전자에서 전력 손실은 전도 손실과 스위칭 손실에 의해 발생한다. 전도 손실은 반도체 소자의 순방향 전압 강하에 의해 정의된다. 스위칭 손실은 트랜지스터의 스위칭 속도, 다이오드의 역회복 동작, 직렬 인덕턴스, 추가적인 기생 효과 등에 의존한다.

전력·전자에서 전력 손실은 전도 손실과 스위칭 손실에 의해 발생한다. 전도 손실은 반도체 소자의 순방향 전압 강하에 의해 정의된다. 스위칭 손실은 트랜지스터의 스위칭 속도, 다이오드의 역회복 동작, 직렬 인덕턴스, 추가적인 기생 효과 등에 의존한다.

턴온

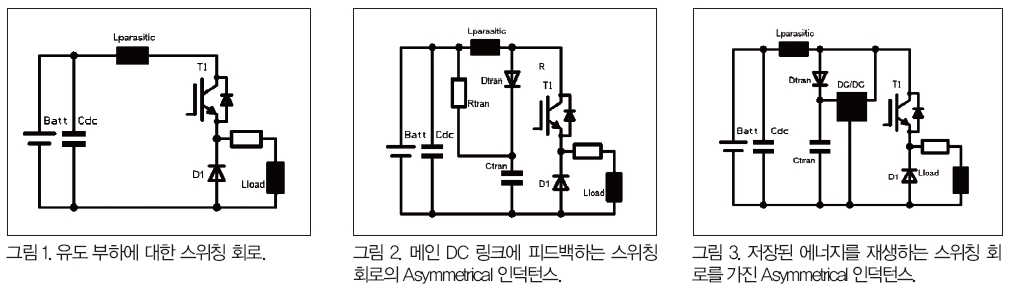

유도부하 시스템(그림 1)에서 프리휠링 다이오드는 턴온으로 동작하고 출력 전압은 DC- 버스 전압과 동일하다. 바로 동작을 시작하는 트랜지스터에는 곧 최대 전류가 걸릴 것이고 출력전압은 DC+ 버스로 증가할 것이다. 여기에서 다이오드는 역전압에 직면하면서 반대 방향으로 작동하게 된다. 이것은 다이오드의 손실(EREC)을 초래하며, 트랜지스터의 전류를 증가시킨다. 이 전류 피크는 종종 전자파의 근본 원인이 된다. 다이오드가 완전히 회복되고 차단된 후에, 트랜지스터의 전류는 출력전류의 레벨로 떨어질 것이다. 턴온 프로세스는 이 과정을 거쳐 완료된다. 트랜지스터 직렬 인덕턴스의 증가는 턴온 손실을 줄이는 데 큰 역할을 한다.

턴오프

턴오프에서 트랜지스터 전압은 DC+ 버스 전압까지 상승할 것이다. 다이오드는 출력전류로 대체될 것이다. 과전압은 추가적인 손실을 일으키는 원인이 되고 트랜지스터를 파괴시킬 수 있는 위험요소가 된다. 전압 피크가 턴오프의 속도에 의존함으로써 빨라진 트랜지스터의 사용은 인덕턴스와 최대전류에 의해 제한된다.

턴오프에서 트랜지스터 전압은 DC+ 버스 전압까지 상승할 것이다. 다이오드는 출력전류로 대체될 것이다. 과전압은 추가적인 손실을 일으키는 원인이 되고 트랜지스터를 파괴시킬 수 있는 위험요소가 된다. 전압 피크가 턴오프의 속도에 의존함으로써 빨라진 트랜지스터의 사용은 인덕턴스와 최대전류에 의해 제한된다.

낮은 유도성 모듈 기술

낮은 유도성을 가진 모듈 기술을 통해 빠른 속도와 높은 전류 모듈의 안정적인 턴오프 실현이 가능해진다. 더불어 턴오프시 스위칭 손실 감소의 효과까지 달성할 수 있다.

턴오프에서 전압 오버슈트를 감소시키는 것은 빠른 부품을 사용할 수 있게 해준다. 인덕턴스의 감소는 턴온에서 스위칭 손실을 감소시키지는 않는다. 턴오프 손실은 감소하겠지만 트랜지스터, 턴온 손실, 그리고 다이오드의 역회복 손실은 더욱 증가할 것이다. 낮은 유도성을 가진 회로의 효율은 빠른 구성요소의 사용으로 증가할 것이다. 전자파의 증가 없이 턴온 손실을 낮추는 것은 초고속 프리휠링 다이오드를 필요로 한다.

턴오프에서 전압 오버슈트를 감소시키는 것은 빠른 부품을 사용할 수 있게 해준다. 인덕턴스의 감소는 턴온에서 스위칭 손실을 감소시키지는 않는다. 턴오프 손실은 감소하겠지만 트랜지스터, 턴온 손실, 그리고 다이오드의 역회복 손실은 더욱 증가할 것이다. 낮은 유도성을 가진 회로의 효율은 빠른 구성요소의 사용으로 증가할 것이다. 전자파의 증가 없이 턴온 손실을 낮추는 것은 초고속 프리휠링 다이오드를 필요로 한다.

Asymmetrical 인덕턴스

턴온에서 인덕턴스를 증가시키고 턴오프에서 매우 낮은 인덕턴스를 가지게 하기 위해 Asymmetrical 인덕턴스를 이용한다. 이 새로운 스위칭 동작 수행법은 턴온에서 기생 인덕턴스 Lparasitic을 활용하고 턴오프에서 그것을 우회하는 것이다(그림 2). 다이오드 Dtran은 Lparasitic에 저장된 에너지를 턴오프 동안 모듈 내의 커패시터 Ctran에 충전한다.

저장된 에너지는 기생된 저항에서 소모될 때까지 Lpara sitic, Dtran, Rtran을 순환한다(그림 3). 이 회로를 통해 스위칭 손실에서 반도체를 해소할 수 있지만 일부 에너지는 수동 부품에서 소모돼야만 한다. DC-DC 회로로 저장된 에너지의 재생은 효율을 증가하는 옵션이다.

Asymmetrical 인덕턴스에 대한 검증

Asymmetrical 인덕턴스에 대한 검증

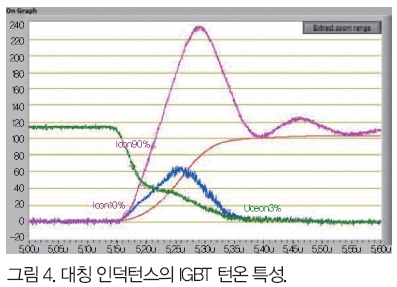

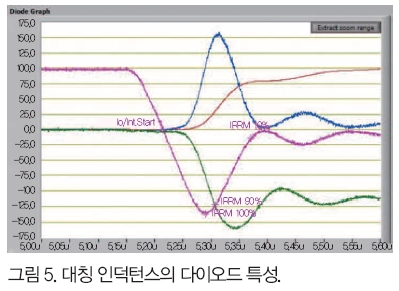

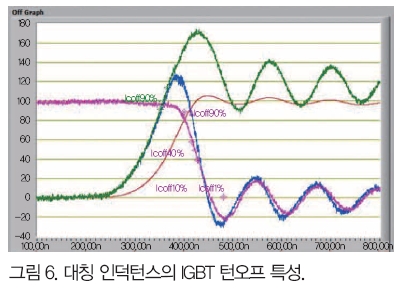

이 아이디어는 전통적인 모듈 배치 및 내부의 스너버 커패시터의 비대칭 배치에 각기 다른 기생 인덕턴스를 구성해서 비교함으로써 검증할 수 있다(그림 4, 5, 6).

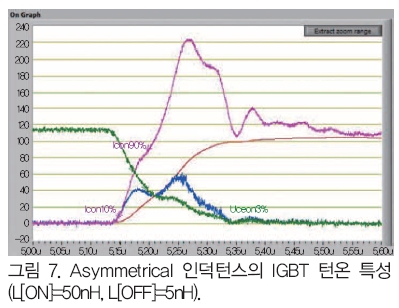

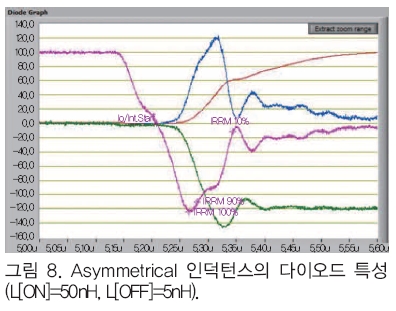

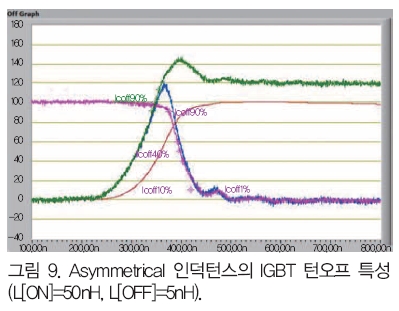

스위칭 손실에서 중요한 것은 전압이 턴오프에서 오버슈트하는 것이다. 특히 낮은 온도에서의 턴오프는 무엇보다 중요하다. 과전류 상황에서 턴오프를 구하는 것은 더 이상 불가능하다. 때문에 동일한 측정은 턴오프에서 5nH, 턴온에서 50nH의 Asymmetrical 인덕턴스로 수행된다(그림 7, 8, 9).

새로운 Asymmetrical 인덕턴스의 스위칭 손실은 낮다. 놀랍게도 턴오프 손실만 감소하는 것이 아니라 모든 스위칭 손실이 감소한다. 회로의 역회복 동작으로 인해 턴온 손실이 감소한다. 턴온에서 트랜지스터 T1의 전류는 다이오드 D1을 통하는 역회복 전류에 의해 증가된다. 완전히 회복된 후 전류는 감소하지만 그 기생 인덕턴스 Lparasitic은 트랜지스터 콜렉터에 과전압을 초래하는 추가적인 에너지를 저장한다. 그 에너지는 커패시터로 흐를 것이다. 이것은 다이오드의 역방향 전류와 트랜지스터의 전압 드롭을 감소시켜 스위칭 손실을 줄이게 된다. Asymmetrical 인덕턴스 회로로 턴온 손실 감소의 장점을 좀 더 끄집어 낼 수 있게 인덕턴스를 증가시키는 것이 가능하다. 이 셋업을 통해 우리는 Asymmetrical 인덕턴스의 장점을 최대한으로 이끌어낸다.

새로운 Asymmetrical 인덕턴스의 스위칭 손실은 낮다. 놀랍게도 턴오프 손실만 감소하는 것이 아니라 모든 스위칭 손실이 감소한다. 회로의 역회복 동작으로 인해 턴온 손실이 감소한다. 턴온에서 트랜지스터 T1의 전류는 다이오드 D1을 통하는 역회복 전류에 의해 증가된다. 완전히 회복된 후 전류는 감소하지만 그 기생 인덕턴스 Lparasitic은 트랜지스터 콜렉터에 과전압을 초래하는 추가적인 에너지를 저장한다. 그 에너지는 커패시터로 흐를 것이다. 이것은 다이오드의 역방향 전류와 트랜지스터의 전압 드롭을 감소시켜 스위칭 손실을 줄이게 된다. Asymmetrical 인덕턴스 회로로 턴온 손실 감소의 장점을 좀 더 끄집어 낼 수 있게 인덕턴스를 증가시키는 것이 가능하다. 이 셋업을 통해 우리는 Asymmetrical 인덕턴스의 장점을 최대한으로 이끌어낸다.

Asymmetrical 인덕턴스의 장점

Asymmetrical 인덕턴스는 특별한 소자를 사용하지 않고도 기본적인 소자가 뛰어나 효율을 향상시킬 수 있다. 턴온 인덕턴스를 증가시키는 것은 트랜지스터의 피크 전류를 감소시킨다. 더불어 이 회로는 값비싼 라미네이티드 버스바가 특별히 필요치 않다. 더불어 전압 스윙과 커패시터의 손실 또한 줄어든다.

Asymmetrical 인덕턴스는 특별한 소자를 사용하지 않고도 기본적인 소자가 뛰어나 효율을 향상시킬 수 있다. 턴온 인덕턴스를 증가시키는 것은 트랜지스터의 피크 전류를 감소시킨다. 더불어 이 회로는 값비싼 라미네이티드 버스바가 특별히 필요치 않다. 더불어 전압 스윙과 커패시터의 손실 또한 줄어든다.

상하위 트랜지스터의 디커플링

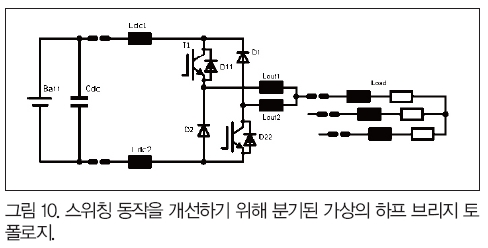

다음 회로(그림 10)는 턴온하는 동안 상호보완적인 스위칭 장치의 출력 커패시턴스 및 교차 전도의 제거로 턴온 손실을 줄이기 위한 솔루션이다. 이 아이디어의 목표는 출력 트랜지스터의 디커플링이다. 다음 회로에서 출력은 두 분기로 구분되고 출력에 연결된 기생 인덕턴스는 소자를 분리하기 위해 활용된다. 이 다이오드는 낮은 유도성 전류 루프를 이루기 위해 직접 연결된다.

멀티 레벨 토폴로지와 병렬연결

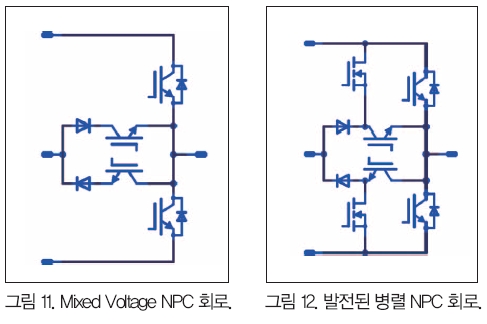

중성점 클램핑(NPC) 인버터나 Mixed Voltage 방식의 NPC 인버터의 멀티레벨 토폴로지의 사용은 스위칭 손실을 줄일 수 있게 스위칭 트랜지스터에서 전압을 절반으로 잘라낸다. 프리휠링 다이오드는 1200V가 아닌 600V와 같은 절반의 전압 크기가 되며, 600V에서는 초고속 역회복 동작이 가능해진다.

중성점 클램핑(NPC) 인버터나 Mixed Voltage 방식의 NPC 인버터의 멀티레벨 토폴로지의 사용은 스위칭 손실을 줄일 수 있게 스위칭 트랜지스터에서 전압을 절반으로 잘라낸다. 프리휠링 다이오드는 1200V가 아닌 600V와 같은 절반의 전압 크기가 되며, 600V에서는 초고속 역회복 동작이 가능해진다.

발전된 병렬연결

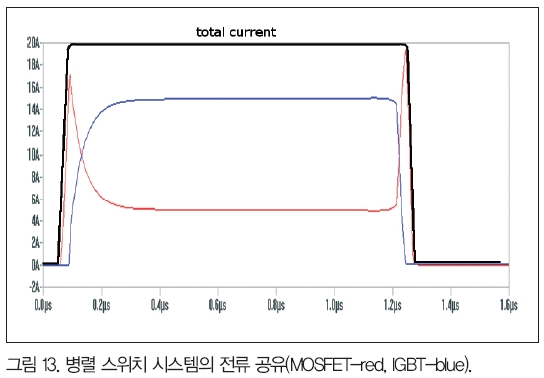

발전된 병렬연결의 목표는 표준 NPC, Mixed Voltage NPC(그림 11), 병렬 스위치 등의 장점을 병합하는 것이다. 발전된 병렬 NPC(그림 12)는 원래 IGBT와 MOSFET를 병렬로 유지하기 위한 아이디어다. 빠른 소자인 MOSFET은 턴온에서 전류에 걸리며, IGBT는 전압 드롭이 낮아서 전류의 대부분이 걸린다. 이 두 MOSFET과 IGBT는 동시에 켜진다. 이를 방지하기 위해 발전된 병렬연결을 통해 IGBT가 턴오프되고 MOSFET는 전류로 점거해 약 100ns 늦게 꺼질 수 있게 된다(그림 13). 발전된 병렬 NPC 토폴로지는 스위칭 손실을 줄여 궁극적으로 효율 상승을 이끈다. 인버터는 16kHz의 PWM 스위칭 주파수에서 현재 99% 이상의 효율에 도달한다. 64kHz 스위칭 주파수 효율조차 98% 이상이다(그림 14).

발전된 병렬연결의 목표는 표준 NPC, Mixed Voltage NPC(그림 11), 병렬 스위치 등의 장점을 병합하는 것이다. 발전된 병렬 NPC(그림 12)는 원래 IGBT와 MOSFET를 병렬로 유지하기 위한 아이디어다. 빠른 소자인 MOSFET은 턴온에서 전류에 걸리며, IGBT는 전압 드롭이 낮아서 전류의 대부분이 걸린다. 이 두 MOSFET과 IGBT는 동시에 켜진다. 이를 방지하기 위해 발전된 병렬연결을 통해 IGBT가 턴오프되고 MOSFET는 전류로 점거해 약 100ns 늦게 꺼질 수 있게 된다(그림 13). 발전된 병렬 NPC 토폴로지는 스위칭 손실을 줄여 궁극적으로 효율 상승을 이끈다. 인버터는 16kHz의 PWM 스위칭 주파수에서 현재 99% 이상의 효율에 도달한다. 64kHz 스위칭 주파수 효율조차 98% 이상이다(그림 14).

.jpg) 조합된 전력 모듈의 사양 및 개념

조합된 전력 모듈의 사양 및 개념

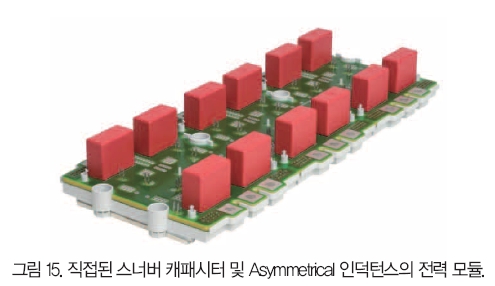

조합된 전력 모듈은 20kHz에서 200KVA 출력을 보이며, IGBT와 MOSFET의 병렬 구성이 가능하다. 뿐만 아니라 해당 스위치의 디커플링을 위한 상단 및 하단 회로의 분리된 출력을 특징으로 한다. 또한 1,200V/500A 정격 전력을 가지고 있으며, 온보드 스너버 커패시터(5nH 턴오프 인덕턴스) 및 DC-DC 재생회로를 가지는 Asymmetrical Parasitic 인덕턴스다(그림 15).

속도와 신뢰성 보장

SiC나 GaN의 스위칭 소자와 같은 새로운 기술의 장점은 표준 Si 소자의 효율성을 높일 수는 있다는 점이다. 기존 전력 설계 디자인의 확장을 위해서는 전력·전자의 기초 부터 인지해야 한다. 낮은 유도성 모듈은 높은 전력 모듈에서 빠르고 신뢰성 있는 턴오프를 보장하며 전압의 오버슈트를 감소시킨다.

부터 인지해야 한다. 낮은 유도성 모듈은 높은 전력 모듈에서 빠르고 신뢰성 있는 턴오프를 보장하며 전압의 오버슈트를 감소시킨다.

매우 낮은 내부 기생 요소를 갖춘 전력 모듈 장치는 매우 비싼 반도체 기술을 사용하지 않고도 스위칭 손실을 줄이기 위한 외부 스트레이 인덕턴스를 활용할 수 있다. Asymmetrical 인덕턴스는 낮은 스위칭 손실과 전자파의 감소, 인버터 기술에 대한 노력을 최소화한다. 여기에서 낮은 유도성 버스바(라미네이티드)는 더 이상 필요하지 않다. DC 링크에 낮은 비용의 케이블을 이용할 수 있다. 증가된 직렬 인덕턴스는 턴온 손실의 추가적인 감소를 일으킨다.

참고문헌

[1] Siemens : “IGBT Fundamentals”, May 1997

[2] Michael Frisch and Temesi Erno : “Advantages of NPC Inverter Topologies with Power Modules”, Vincotech 2009

[3] Michael Frisch and Temesi Erno : “Power Module with Additional Low Inductive Current Path”, Vincotech Germany and Hungary 2009

[4] Wilhelm Rusche and Marco Bassler : “Influence of Stray Inductance on High-Efficiency IGBT Based Inverter Designs”, Infineon Technologies, Warstein, Germany 2010

[5] Peter Haaf, Jon Harper : “Diode Reverse Recovery and its Effect on Switching Losses”, November 2006:

[6] Akira Nabae, Isao Takahasi, Hirofumi Akag i: “A New Neutral-Point-Clamped PWM Inverter”, September/October 1981

[7] Dr.-Ing.Paul Chr. Mourick : “Parasitic Inductivities and Parasitic Oscillations an Overview”, 24. Feb. 2011

[8] Dr.-Ing. Eckart Hoene: ”Parasitic Effects - An overview”, ECPE, Feb. 2011

[9] Helmut Lindner, Dr. Ing Harry Brauer, Dr. Ing. Constans Lehmann “Elektrotechnik”, 1982(page 82)

SOLAR TODAY 편집국 (st@infothe.com)

<저작권자 : 솔라투데이 (http://www.solartodaymag.com/) 무단전재-재배포금지>

![[이슈읽기] 이종석 국정원장 청문회,](/news/thumbnail/202506/65960_75673_3432_v150.jpg)